ISL58328

12

FN6329.2

July 29, 2013

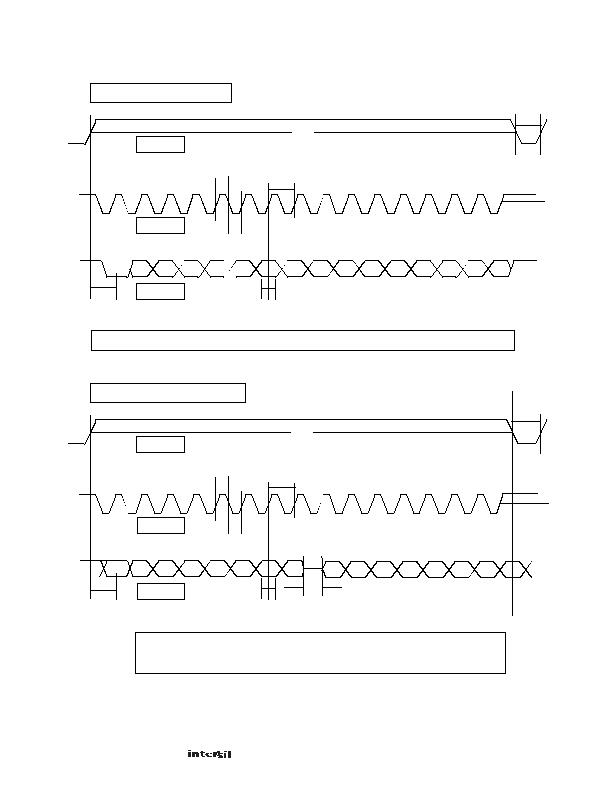

Serial Interface Protocol

WRITING CYCLE INTO ISL58328

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

0

t

CDS

t

CDH

t

CC

tCH

t

CL

t

ERSR

SEN

SCLK

SDATA

t

SREF

R/W BIT, ADDRESS BITS, AND DATA BITS ARE CLOCKED INTO ISL58328 AT RISING EDGE OF SCLK.

R/W

READING CYCLE FROM ISL58328

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

1

t

CDS

t

CDH

t

CC

t

CH

t

CL

t

ERSR

SEN

SCLK

SDATA

t

SREF

Hi-Z

t

CDD

R/W BIT AND ADDRESS BITS ARE CLOCKED INTO ISL58328 AT RISING EDGE OF SCLK.

DATA BITS ARE CLOCKED OUT FROM ISL58328 AT FALLING EDGE OF SCLK.

THE LAST BIT (D0) OF DATA IS CLOCKED BY THE FALLING EDGE OF SEN.

t

EH

t

EH

t

EL

t

EL

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL58334CIZ-T7A

IC SENSOR

LBB315PA-100

LINEAR TRANSDUCER

LDB182G4505C-110

TRANSFORMER BALUN 2.45GHZ 0603

LPD-SOM-CLIP2-THPAD

THERMAL PAD TORPEDO, SOM-M1,M2

M032100

BLUETOOTH/GPS ANTENNA 10X3X1.3MM

M232110-1K

SAVVI CERAMIC IMD GPS BT

M310210-1K

RF ANT BLUETOOTH WIFI 2.4GHZ

M620710-1K

RF ANT SAVVI ISM CHIP

相关代理商/技术参数

ISL58333

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wide Optical Spectrum Laser Power Monitor IC

ISL58333_1110

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Wide Optical Spectrum Laser Power Monitor IC

ISL58333CIZ-T7

功能描述:IC LASER PWR MONITOR 9WLCSP RoHS:是 类别:集成电路 (IC) >> 接口 - 传感器和探测器接口 系列:- 其它有关文件:Automotive Product Guide 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:74 系列:- 类型:触控式传感器 输入类型:数字 输出类型:数字 接口:JTAG,串行 电流 - 电源:100µA 安装类型:表面贴装 封装/外壳:20-TSSOP(0.173",4.40mm 宽) 供应商设备封装:20-TSSOP 包装:管件

ISL58334CIZ-EVAL

制造商:Intersil Corporation 功能描述:ISL58334CIZ EVALUATION BOARD - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ISL58334 制造商:Intersil Corporation 功能描述:ISL6208ACBZ- MSFT DRVR W/DIODE EMULATN

ISL58334CIZ-T7

功能描述:IC LASER PWR MONITOR 3V 9CSP RoHS:是 类别:传感器,转换器 >> 专用 系列:- 标准包装:40 系列:*

ISL58334CIZ-T7A

功能描述:IC SENSOR RoHS:是 类别:传感器,转换器 >> 专用 系列:* 标准包装:40 系列:*

ISL58344

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Segment Photo Sensor IC Single +3.3V Power Supply

ISL58344CIZ-EVAL

制造商:Intersil Corporation 功能描述:ISL58344CIZ EVALUATION BOARD - Bulk 制造商:Intersil Corporation 功能描述:BOARD EVAL FOR ISL58344 制造商:Intersil 功能描述:ISL6224 SINGLE PWM EVAL BRD 4 MOBL APPS